ARM-v8�ܹ�����64λ�ܹ������¼���ARM-v7�ܹ���ARM-v8�ܹ�֧���������͵�ARMָ���һ����Aarch64λָ���һ����Aarch32λָ����������������͵�ָ���ÿ��ָ����Ȼ�����֣�4�ֽڣ����롣��������ָ��ı��������ǹ����Ĵ�����λ����ͬ��Aarch32λָ�ʹ��32bit�����Ĵ�������Aarch64λָ�ʹ��64bit�����Ĵ�����

�Ĵ�����������

| � | ���� | ||

| 32-bit | Wn��ͨ�ã� | WZR��0�Ĵ����� | WSP����ջָ�룩 |

| 64-bit | Xn��ͨ�ã� | XZR��0�Ĵ����� | SP����ջָ�룩 |

AArch32��Ҫ�Ĵ���

| �Ĵ������� | Bit | ���� |

| R0-R14 | 32bit | ͨ�üĴ���������ARM������ʹ��������ܵ�R13��R14��R15����ͨ�üĴ���ʹ��. |

| SP_x | 32bit | ͨ����R13Ϊ��ջָ�룬����User��Sysģʽ�⣬��������ģʽ�¶��ж�Ӧ��SP_x�Ĵ�����x ={ und/svc/abt/irq/fiq/hyp/mon} |

| LR_x | 32bit | ��R14Ϊ���ӼĴ���������User��Sysģʽ�⣬��������ģʽ�¶��ж�Ӧ��SP_x�Ĵ�����x ={ und/svc/abt/svc/irq/fiq/mon},���ڱ������������Ϣ��ַ��AArch32�����£�Ҳ���ڱ����쳣���ص�ַ��Ҳ��˵LR��ELR�ǹ���һ����AArch64���Ƕ�����. |

| ELR_hyp | 32bit | Hyp mode�����е��쳣���ӼĴ����������쳣����Hyp modeʱ���쳣��ַ |

| PC | 32bit | ͨ����R15Ϊ���������PCָ�룬AArch32 ��PCָ��ȡָ��ַ����ִ��ָ���ַ+8��AArch64��PC��ȡʱָ��ǰָ���ַ. |

| CPSR | 32bit | ��¼��ǰPE������״̬����,CPSR.M[4:0]��¼����ģʽ��AArch64��ʹ��PSTATE���� |

| APSR | 32bit | Ӧ�ó���״̬�Ĵ�����EL0�¿���ʹ��APSR���ʲ���PSTATEֵ |

| SPSR_x | 32bit | ��CPSR�ı��ݣ�����User��Sysģʽ�⣬��������ģʽ�¶��ж�Ӧ��SPSR_x�Ĵ�����x ={ und/svc/abt/irq/fiq/hpy/mon}��ע�⣺��Щģʽֻ������32bit���л��� |

| HCR | 32bit | EL2���У�HCR.{TEG,AMO,IMO,FMO,RW}����EL0/EL1���쳣·�� |

| SCR | 32bit | EL3���У�SCR.{EA,IRQ,FIQ,RW}����EL0/EL1/EL2���쳣·�ɣ�ע��EL3ʼ�ղ���·�� |

| VBAR | 32bit | ���������쳣�����Hyp mode & ��Monitor mode����ת��������ַ |

| HVBAR | 32bit | ���������쳣����Hyp mode����ת��������ַ |

| MVBAR | 32bit | ���������쳣����Monitor mode����ת��������ַ |

| ESR_ELx | 32bit | �����쳣����ELxʱ���쳣�ۺ���Ϣ�������쳣����EC�ȣ�����ͨ��ECֵ�ж��쳣class |

| PSTATE | ����һ���Ĵ������DZ��浱ǰPE״̬��һ��Ĵ���ͳ�ƣ����пɷ��ʼĴ����У�PSTATE.{NZCV,DAIF,CurrentEL,SPSel},����ARMv8�������ݣ���Ҫ����64bit������ |

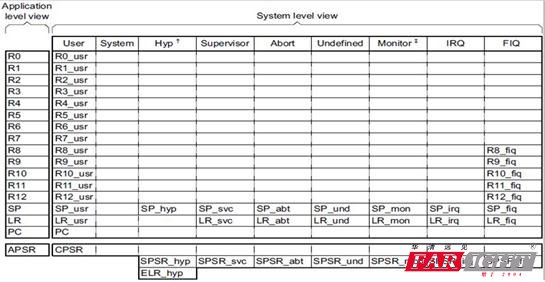

A32״̬�¼Ĵ�����֯

• ��ν��banked

register ��ָһ���Ĵ����ڲ�ͬģʽ���ж�Ӧ��ͬ�ļĴ���������SP����abortģʽ����SP_bat����Undģʽ��SP_und,��iqrģʽ����SP_irq�ȣ��������ģʽ����Զ��л�ӳ�䵽����ģʽ�¶�Ӧ�ļĴ���.

• R0-R7����ν�ķ�banked register��R8-R14����ν��banked register

4.1.1 T32״̬�¼Ĵ�����֯

|

A32ʹ�� Rd/Rn����λ��4λ |

T32-32bitʹ�� Rd/Rn����λ��4λ |

T32-16bitʹ�� Rd/Rn����λ��3λ |

| R0 | R0 | R0 |

| R1 | R1 | R1 |

| R2 | R2 | R2 |

| R3 | R3 | R3 |

| R4 | R4 | R4 |

| R5 | R5 | R5 |

| R6 | R6 | R6 |

| R7 | R7 | R7 |

| R8 | R8 | ������˵T32-16bit��û��R8��R12����������ָ����ܷ��ʵ�,16bitָ���Rd/Rn����λֻ��3λ������Rx��Χ��R0-R7 |

| R9 | R9 | |

| R10 | R10 | |

| R11 | R11 | |

| R12 | R12 | |

| SP (R13) | SP (R13) | SP (R13) |

| LR (R14) | LR (R14) //M | LR (R14) //M |

| PC (R15) | PC (R15) //P | PC (R15) //P |

| CPSR | CPSR | CPSR |

| SPSR | SPSR | SPSR |

AArch64��Ҫ�Ĵ���

| �Ĵ������� | Bit | ���� |

| X0-X30 | 64bit | ͨ�üĴ������������Ҫ���Ե���32bitʹ�ã�WO-W30 |

| LR (X30) | 64bit | ͨ����X30Ϊ�������ӼĴ�����������ת������Ϣ��ַ |

| SP_ELx | 64bit | ��PSTATE.M[0] ==1����ÿ��ELxѡ��SP_ELx������ѡ��ͬһ��SP_EL0 |

| ELR_ELx | 64bit | �쳣���ӼĴ����������쳣����ELx���쳣��ַ��x={0,1,2,3}�� |

| PC | 64bit | ������������׳�PCָ�룬����ָ��Ҫִ�е���һ��ָ�� |

| SPSR_ELx | 32bit | �Ĵ������������ELx��PSTATE״̬��Ϣ |

| NZCV | 32bit | �������ʵķ��ű�־λ |

| DIAF | 32bit | �ж�ʹ��λ��D-Debug��I-IRQ��A-SError��F-FIQ ����0���� |

| CurrentEL | 32bit | ��¼��ǰ�����ĸ�Exception level |

| SPSel | 32bit | ��¼��ǰʹ��SP_EL0����SP_ELx��x= {1,2,3} |

| HCR_EL2 | 32bit | HCR_EL2.{TEG,AMO,IMO,FMO,RW}����EL0/EL1���쳣·�� ��1���� |

| SCR_EL3 | 32bit | SCR_EL3.{EA,IRQ,FIQ,RW}����EL0/EL1/EL2���쳣·�� ��1���� |

| ESR_ELx | 32bit | �����쳣����ELxʱ���쳣�ۺ���Ϣ�������쳣����EC��. |

| VBAR_ELx | 64bit | ���������쳣����ELx����ת��������ַ x={0,1,2,3} |

| PSTATE | ����һ���Ĵ������DZ��浱ǰPE״̬��һ��Ĵ���ͳ�ƣ����пɷ��ʼĴ����У�PSTATE.{NZCV,DAIF,CurrentEL,SPSel},����ARMv8��������,64bit�´���CPSR |

64��32λ�Ĵ�����ӳ���ϵ

| 64-bit | 32-bit |

64-bit OS Runing AArch32 App |

64-bit | 32-bit |

| X0 | R0 | X20 | LR_adt | |

| X1 | R1 | X21 | SP_abt | |

| X2 | R2 | X22 | LR_und | |

| X3 | R3 | X23 | SP_und | |

| X4 | R4 | X24 | R8_fiq | |

| X5 | R5 | X25 | R9_fiq | |

| X6 | R6 | X26 | R10_fiq | |

| X7 | R7 | X27 | R11_fiq | |

| X8 | R8_usr | X28 | R12_fiq | |

| X9 | R9_usr | X29 | SP_fiq | |

| X10 | R10_usr | X30(LR) | LR_fiq | |

| X11 | R11_usr | SCR_EL3 | SCR | |

| X12 | R12_usr | HCR_EL2 | HCR | |

| X13 | SP_usr | VBAR_EL1 | VBAR | |

| X14 | LR_usr | VBAR_EL2 | HVBAR | |

| X15 | SP_hyp | VBAR_EL3 | MVBAR | |

| X16 | LR_irq | ESR_EL1 | DFSR | |

| X17 | SP_irq | ESR_EL2 | HSR | |

| X18 | LR_svc | |||

| X19 | SP_svc |

�ȵ�����

�����ˣ�Xena

�����ˣ�Scorpio

�����ˣ�Wing

-

�Ƽ����ܡ�����δ��

�Ƽ����ܡ�����δ��

-

��ע����

��ע����Զ��

��ע����ѧԺ

��ע����Զ��

��ע����ѧԺ

��ע����Զ��

��ע����ѧԺ

��ע����Զ��

��ע����ѧԺ

����

����

��ǰλ��:

��ǰλ��:  �߶˿γ�

�߶˿γ�

ԤԼ��ʦ

ԤԼ��ʦ

�������

�������

ȫ����ѯ���ߣ�400-611-6270

ȫ����ѯ���ߣ�400-611-6270